“LTT-MX6-SOM200硬件设计指导要求”的版本间的差异

| (未显示同一用户的13个中间版本) | |||

| 第243行: | 第243行: | ||

|- | |- | ||

| 34 || TOUCH_nINT || TOUCH_nINT || R6 || I||3.3V | | 34 || TOUCH_nINT || TOUCH_nINT || R6 || I||3.3V | ||

| + | |- | ||

| + | | 35 || TOUCH_RST || TOUCH_RST || D16 || O||3.3V | ||

| + | |- | ||

| + | | 36 || TOUCH_SCL || TOUCH_SCL|| rowspan=2 |连接至I2C3 || IO||3.3V | ||

| + | |- | ||

| + | | 37 || TOUCH_SDA || TOUCH_SDA || IO||3.3V | ||

| + | |- | ||

| + | | 38 || rowspan=3 colspan=3 align="center"|电源地 || rowspan=3 |I||rowspan=3 |0V | ||

| + | |- | ||

| + | | 39 | ||

| + | |- | ||

| + | | 40 | ||

|- | |- | ||

|} | |} | ||

| 第248行: | 第260行: | ||

组内信号线要求做等长处理。 | 组内信号线要求做等长处理。 | ||

| + | ===SATA硬盘接口=== | ||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | ! Pin Number !! Description !! CPU Pin Name !! CPU !! Direction !! Voltage | ||

| + | |- | ||

| + | | 121 || Positive Receive Signal || SATA_RXP || B14 || I || rowspan=4|2.5V | ||

| + | |- | ||

| + | | 120 || Negative Receive Signal || SATA_RXN || A14 || I | ||

| + | |- | ||

| + | | 122 || Positive Transmit Signal || SATA_TXP || A12 || O | ||

| + | |- | ||

| + | | 123 || Negative Transmit Signal || SATA_TXN || B12 || O | ||

| + | |} | ||

| + | '''设计要求''' | ||

| + | |||

| + | SATA差分信号对之间走线要求做等长处理,采用尽可能小封装的耦合电容,电容的位置要尽量靠近连接器,差分信号的阻抗控制在100ohm。 | ||

| + | |||

| + | ===USB接口=== | ||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | ! Pin Number !! Description !! CPU Pin Name !! CPU !! Direction !! Voltage | ||

| + | |- | ||

| + | | 131|| rowspan=2|USB HOST || USB_H1_DN || F10 || IO || rowspan=4| | ||

| + | |- | ||

| + | | 130 || USB_H1_DP || E10 || IO | ||

| + | |- | ||

| + | | 135 || rowspan=2|USB OTG || USB_OTG_DN || B6 || IO | ||

| + | |- | ||

| + | | 134 || USB_OTG_DP || A6 || IO | ||

| + | |- | ||

| + | | '''132''' || rowspan=2|USB_OTG_ID || '''GPIO01''' || T4 ||rowspan=2| I ||rowspan=6|3.3V | ||

| + | |- | ||

| + | | 14 || ENET_RX_ER || W23 | ||

| + | |- | ||

| + | | '''49''' || rowspan=2|USB_OTG_OC || '''EIM_DATA21''' || H20 || rowspan=2| I | ||

| + | |- | ||

| + | | 190 || KEY_COL4 || T6 | ||

| + | |- | ||

| + | | '''61''' || rowspan=2|USB_OTG_PWR || '''EIM_DATA22''' || E23 || rowspan=2|O | ||

| + | |- | ||

| + | | 189 || KEY_ROW4 || V5 | ||

| + | |} | ||

| + | '''设计要求''' | ||

| + | |||

| + | 尽可能缩短走线长度,尽可能的减少在USB高速信号线上的过孔数和拐角,从而可以更好的做到阻抗的控制,避免信号的反射。在布线时,要做到差分信号走线的长度匹配。控制USB差分信号对之间的布线间距,要确保90 ohm的差分阻抗。 | ||

| + | ===SD接口=== | ||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | ! Pin Number !! Description !! CPU Pin Name !! CPU !! Direction !! Voltage | ||

| + | |- | ||

| + | | 89 || rowspan=6|SD1 Signal || SD1_CMD || B21 || I || rowspan=6|3.3V | ||

| + | |- | ||

| + | | 90 || SD1_CLK || D20 || O | ||

| + | |- | ||

| + | | 91 || SD1_DATA0 || A21 || IO | ||

| + | |- | ||

| + | | 92 || SD1_DATA1 || C20 || IO | ||

| + | |- | ||

| + | | 93 || SD1_DATA2 || E19 || IO | ||

| + | |- | ||

| + | | 94 || SD1_DATA3 || F18 || IO | ||

| + | |- | ||

| + | | 83 || rowspan=6|SD2 Signal || SD2_CMD || F19 || IO || rowspan=6|3.3V | ||

| + | |- | ||

| + | | 84 ||SD2_CLK ||SD2_CLK||O | ||

| + | |- | ||

| + | |85 || SD2_DATA0 || A22 || IO | ||

| + | |- | ||

| + | | 86 || SD2_DATA1 ||E20 || IO | ||

| + | |- | ||

| + | | 87 || SD2_DATA2 || A23 || IO | ||

| + | |- | ||

| + | | 88 || SD2_DATA3 || B22 || IO | ||

| + | |- | ||

| + | | 110 || rowspan=10|SD3 Signal || SD3_CMD || B13 || IO || rowspan=10|3.3V | ||

| + | |- | ||

| + | | 109 || SD3_CLK || D14|| O | ||

| + | |- | ||

| + | | 111 || SD3_DATA0 || E14 ||IO | ||

| + | |- | ||

| + | | 112 || SD3_DATA1 || F14 || IO | ||

| + | |- | ||

| + | |113 || SD3_DATA2 || A15|| IO | ||

| + | |- | ||

| + | | 114 || SD3_DATA3 || B15 || IO | ||

| + | |- | ||

| + | | 115 || SD3_DATA4 || D13 || IO | ||

| + | |- | ||

| + | | 116 || SD3_DATA5 || C13 || IO | ||

| + | |- | ||

| + | | 117 || SD3_DATA6 || E13 || IO | ||

| + | |- | ||

| + | | 118 || SD3_DATA7 || F13 || IO | ||

| + | |- | ||

| + | |} | ||

| + | ===PCIE接口=== | ||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | !Pin Number !! Description !! CPU Pin Name !! CPU !! Direction !! Voltage | ||

| + | |- | ||

| + | | 141 || Positive Receive Signal || PCIE_RXP || B2 || I || rowspan=4|2.5V | ||

| + | |- | ||

| + | | 140 || Negative Receive Signal || PCIE_RXM || B1 || I | ||

| + | |- | ||

| + | | 139 || Positive Transmit Signal || PCIE_TXP || B3 || O | ||

| + | |- | ||

| + | | 138 || Negative Transmit Signal || PCIE_TXM || A3 || O | ||

| + | |} | ||

| + | '''设计要求''' | ||

| + | |||

| + | PCIE信号为差分信号,布线时要注意减少有害串扰的影响和电磁干扰(EMI)的影响。 | ||

| + | ===AUD音频接口=== | ||

| + | 核心板提供音频信号,可以使用WM8962芯片进行音频编解码,这是一款低功耗、高性能的立体音频编解码器。它支持单端输入,录音通道支持自动增量控制(AGC),且内置滤波电路。同时支持两路单端输出和两路差分高功率输出。I2C信号用于配置芯片寄存器,I2S用于音频数据传输,系统默认使用I2C1和I2S3来连接WM8962,如需使用请参照我司的参考设计,请使用者谨记。 | ||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | ! Pin Number !! Description !! CPU Pin Name !! CPU !! Direction !! Voltage | ||

| + | |- | ||

| + | | 179 || rowspan=4|AUD3 Signal || AUD3_TXC || N1 || IO || rowspan=4|1.8V | ||

| + | |- | ||

| + | | 178 || AUD3_TXFS || N4 || IO | ||

| + | |- | ||

| + | | 180 || AUD3_TXD || P2 || IO | ||

| + | |- | ||

| + | | 177 || AUD3_RXD || N3 || IO | ||

| + | |- | ||

| + | | 83 || AUD4_RXC || SD2_CMD || F19 || IO || rowspan=24|3.3V | ||

| + | |- | ||

| + | | 85 || AUD4_RXC ||SD2_DATA0 || A22 ||IO | ||

| + | |- | ||

| + | | 84 || AUD4_RXC || SD2_CLK || C21 ||IO | ||

| + | |- | ||

| + | | 88 || AUD4_TXC ||SD2_DATA3 || B22 || IO | ||

| + | |- | ||

| + | | 87 || AUD4_TXD|| SD2_DATA2 || A23|| IO | ||

| + | |- | ||

| + | | 86 || AUD4_TXFS || SD2_DATA1 || E20 ||IO | ||

| + | |- | ||

| + | | 58 ||AUD5_RXC|| EIM_DATA25 || G22||IO | ||

| + | |- | ||

| + | | 196 || AUD5_RXD ||KEY_ROW1|| U6||IO | ||

| + | |- | ||

| + | | 60 ||AUD5_RXFS || EIM_DATA24 || F22 ||IO | ||

| + | |- | ||

| + | | 199 || AUD5_TXC|| KEY_COL0 || W5 ||IO | ||

| + | |- | ||

| + | | 198 || AUD5_TXD|| KEY_ROW0KEY_COL1||V6||IO | ||

| + | |- | ||

| + | | 197 || AUD5_TXFS|| KEY_COL1||U7||IO | ||

| + | |} | ||

| + | '''设计要求''' | ||

| + | |||

| + | 保持音频信号线尽可能短,并尽量远离干扰源,信号线做到组内等长。 | ||

| + | ===百兆以太网接口=== | ||

| + | LTT_MX6_SOM200核心板引出两组以太网的接口,分别为百兆以太网和千兆以太网接口,由于IMX6系列的芯片不支持百兆以太网和千兆以太网同时使用,所以目前两种接口同时只能使用一种,请使用者多加注意。 | ||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | ! Pin Number !! Description !! CPU Pin Name !! CPU !! Direction !! Voltage | ||

| + | |- | ||

| + | | 19 || ENET_MDC || '''ENET_MDC''' || '''V20''' || O || rowspan=11|3.3V | ||

| + | |- | ||

| + | | 16 ||ENET_MDIO|| '''ENET_MDIO'''||'''V23'''||IO | ||

| + | |- | ||

| + | | 18 ||rowspan=9|Enet Signal || ENET_RXD0 || W21 ||I | ||

| + | |- | ||

| + | | 13 || ENET_RXD1 ||W22|| I | ||

| + | |- | ||

| + | | 21 ||ENET_CRS_DV ||U21 || I | ||

| + | |- | ||

| + | | 22 ||ENET_TXD0 || U20 || O | ||

| + | |- | ||

| + | | 17 || ENET_TXD1 || W20 ||O | ||

| + | |- | ||

| + | |20 || ENET_TX_EN || V21 ||O | ||

| + | |- | ||

| + | | 182 ||ENET_nRST || R1 || O | ||

| + | |- | ||

| + | | 15 || ENET_REF_CLK || V22 || O | ||

| + | |- | ||

| + | | 107 || ENET_nINT || A16 ||I | ||

| + | |} | ||

| + | ===千兆以太网接口=== | ||

| + | LTT_MX6_SOM200核心板引出两组以太网的接口,分别为百兆以太网和千兆以太网接口,由于IMX6系列的芯片不支持百兆以太网和千兆以太网同时使用,所以目前两种接口同时只能使用一种,请使用者多加注意。 | ||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | ! Pin Number !! Description !! CPU Pin Name !! CPU !! Direction !! Voltage | ||

| + | |- | ||

| + | | 71|| rowspan=12|RGMII Signal || RGMII_RXD3 || D23 || I|| rowspan=12|1.5V | ||

| + | |- | ||

| + | |72|| RGMII_RXDV ||D22 || I | ||

| + | |- | ||

| + | | 73 || RGMII_TXEN || C23 || O | ||

| + | |- | ||

| + | | 74 || RGMII_TXD0 || C22 || O | ||

| + | |- | ||

| + | | 75 || RGMII_TXD1 || F20 || O | ||

| + | |- | ||

| + | | 76 || RGMII_TXD2 || E21 || O | ||

| + | |- | ||

| + | | 77 || RGMII_TXCLK || D21 || O | ||

| + | |- | ||

| + | | 78 || RGMII_RXD0 || C24 || I | ||

| + | |- | ||

| + | | 79 || RGMII_RXCLK || B25|| O | ||

| + | |- | ||

| + | | 80 || RGMII_RXD2 || B24 || I | ||

| + | |- | ||

| + | | 81 ||RGMII_TXD3 || D23 || O | ||

| + | |- | ||

| + | | 82 || RGMII_RXD1 || B23 || O | ||

| + | |} | ||

| + | '''设计要求:''' | ||

| + | |||

| + | 保持RGMII信号线尽可能短,并尽量远离干扰源,信号线做到组内等长。 | ||

| + | |||

| + | ===CAN总线接口=== | ||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | ! Pin Number !! Description !! CPU Pin Name !! CPU !! Direction !! Voltage | ||

| + | |- | ||

| + | | 191 || CAN1_RX || '''GPIO08''' || '''R5''' || I || rowspan=12|3.3V | ||

| + | |- | ||

| + | | 192 || CAN1_TX ||'''GPIO07''' || '''R3''' || O | ||

| + | |- | ||

| + | | 189 || CAN2_RX || '''KEY_ROW4''' || '''V5''' || I | ||

| + | |- | ||

| + | | 190 || CAN2_TX || '''KEY_COL4''' || '''T6''' || O | ||

| + | |} | ||

| + | '''设计要求:''' | ||

| + | |||

| + | 布线时要注意控制收发器转换后差分对信号等长。注意给CAN总线匹配终端电阻。 | ||

| + | |||

| + | ===SPI接口=== | ||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | ! Pin Number !! Description !! CPU Pin Name !! CPU !! Direction !! Voltage | ||

| + | |- | ||

| + | | 63 || CSPI2_MISO || '''EIM_OE''' || '''J24''' || IO || rowspan=6|3.3V | ||

| + | |- | ||

| + | | 53 ||CSPI2_MOSI || '''EIM_CS1''' || '''J23''' || IO | ||

| + | |- | ||

| + | | 50 || CSPI2_RDY || EIM_A25 || H19 ||I | ||

| + | |- | ||

| + | | 62 || CSPI2_CLK || '''EIM_CS0''' || '''H24'''||IO | ||

| + | |- | ||

| + | | 46 || CSPI2_CS0 || '''EIM_RW''' || '''K20''' || IO | ||

| + | |- | ||

| + | | 52 || CSPI2_CS1 || '''EIM_LBA''' || '''K22''' || IO | ||

| + | |- | ||

| + | | 61 || CSPI4_MISO || EIM_D22 || E23 || IO || rowspan=7|3.3V | ||

| + | |- | ||

| + | | 57 || CSPI4_MOSI || EIM_D28|| G23 || IO | ||

| + | |- | ||

| + | | 59 || CSPI4_RDY|| EIM_EB3 || F23 ||I | ||

| + | |- | ||

| + | | 49 ||CSPI4_CLK || EIM_D21 || H20 || IO | ||

| + | |- | ||

| + | | 48 || CSPI4_CS0 || '''EIM_DATA29''' || '''J19''' || IO | ||

| + | |- | ||

| + | | 60 || CSPI4_CS2 || EIM_DATA24 || F22 || IO | ||

| + | |- | ||

| + | | 58 || CSPI4_CS3 || EIM_DATA25 || G22|| IO | ||

| + | |} | ||

| + | ===12C接口=== | ||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | ! Pin Number !! Description !! CPU Pin Name !! CPU !! Direction !! Voltage | ||

| + | |- | ||

| + | | 175 || I2C1 Serial Data || I2C1_SDA || N6 || IO || rowspan=2|1.8V | ||

| + | |- | ||

| + | |176 || I2C1 Serial Clock || I2C1_SCL || N5 || IO | ||

| + | |- | ||

| + | | 187 || I2C2 Serial Data || I2C2_SDA || T7 || IO || rowspan=2|3.3V | ||

| + | |- | ||

| + | | 188 || I2C2 Serial Clock || I2C2_SCL || U5 || IO | ||

| + | |- | ||

| + | | 194 || I2C3 Serial Data || I2C3_SDA || T3 || IO || rowspan=2|3.3V | ||

| + | |- | ||

| + | | 195 || I2C3 Serial Clock || I2C3_SCLL || R7 ||IO | ||

| + | |} | ||

| + | ===CSI摄像头接口=== | ||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | ! Pin Number !! Description !! CPU Pin Name !! CPU !! Direction !! 电压 | ||

| + | |- | ||

| + | | 107 || rowspan=8| IPU CSI Data Signal|| CSIO_DAT12 || M2 || I || rowspan=11|2.5V | ||

| + | |- | ||

| + | | 105 || CSIO_DAT13 || L1 || I | ||

| + | |- | ||

| + | | 99 ||CSIO_DAT14 || M4|| I | ||

| + | |- | ||

| + | | 115 || CSIO_DAT15 || M5 || I | ||

| + | |- | ||

| + | | 97 || CSIO_DAT16 || L4 || I | ||

| + | |- | ||

| + | | 95 || CSIO_DAT17 || L3 || I | ||

| + | |- | ||

| + | | 103|| CSIO_DAT18 || M6 || I | ||

| + | |- | ||

| + | | 101 || CSIO_DAT19 || L6 || I | ||

| + | |- | ||

| + | | 113 || IPU CSI Hsync Signal || CSI0_HSYNCH || P4 || I | ||

| + | |- | ||

| + | | 109 || IPU CSI Vsync Signal|| CSI0_VSYNCH || N2 || I | ||

| + | |- | ||

| + | | 111 || IPU CSI Pixclk Signal || CSI0_PIXCLK || P1 || I | ||

| + | |- | ||

| + | |} | ||

| + | '''设计要求''' | ||

| + | |||

| + | CSI-MCLK和CSI-PCLK需要各自包地,并保证较少的换层连接到摄像头连接器,保证连接器周围信号地的完整性 | ||

| + | ===MIPI摄像头接口=== | ||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | ! Pin Number !! Description !! CPU Pin Name !! CPU !! Direction !! 电压 | ||

| + | |- | ||

| + | | 141 || rowspan=8|D-Phy Differential Data ||CSI_D3M || F2 ||IO ||rowspan=10|2.5V | ||

| + | |- | ||

| + | | 142 || CSI_D3P || F1 || IO | ||

| + | |- | ||

| + | | 143 || CSI_D2M || E1 || IO | ||

| + | |- | ||

| + | | 144 || CSI_D2P || E2 || IO | ||

| + | |- | ||

| + | | 145 || CSI_D1M || D1 ||IO | ||

| + | |- | ||

| + | | 146 || CSI_D1P || D2 || IO | ||

| + | |- | ||

| + | | 147 || CSI_D0M || E4 || IO | ||

| + | |- | ||

| + | | 148 || CSI_D0P || E3 || IO | ||

| + | |- | ||

| + | | 149 || rowspan=2|D-Phy Differential Clock || CSI_CLKM || F4 ||IO | ||

| + | |- | ||

| + | | 150 || CSI_CLKP || F3 ||IO | ||

| + | |} | ||

| + | |||

| + | '''设计要求''' | ||

| + | |||

| + | MIPI信号线下方一定要有参考层(推荐用地层),且一定要保证参考层的连续性。MIPI线对之间以及线对与线对之间的长度误差注意控制,MIPI信号线尽量不要打过孔。 | ||

| + | ===UART接口=== | ||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | ! Pin Number !! Description !! CPU Pin Name !! CPU !! Direction!! 电压 | ||

| + | |- | ||

| + | | 173 || UART1_RX || UART1_RX || M3 || I ||rowspan=2|1.8V | ||

| + | |- | ||

| + | | 174 || UART1_TX || UART1_TX || M1 || O | ||

| + | |- | ||

| + | | 57 || UART2_CTS || '''EIM_D28''' || '''G23''' || O || rowspan=4|3.3V | ||

| + | |- | ||

| + | | 48 || UART2_RTS || '''EIM_D29''' || '''J19''' || I | ||

| + | |- | ||

| + | | 68 || UART2_RXD || '''EIM_D27'''|| '''E25''' || I | ||

| + | |- | ||

| + | | 69 || UART2_TXD || '''EIM_D26''' ||'''E24''' || O | ||

| + | |- | ||

| + | | 70 || UART3_CTS || '''EIM_D23''' || '''D25''' || O || rowspan=4|3.3V | ||

| + | |- | ||

| + | | 44 || UART3_RTS || '''EIM_D31''' || H21 || I | ||

| + | |- | ||

| + | | 58 || UART3_RXD || UART3_RXD || G22 || I | ||

| + | |- | ||

| + | | 60 || UART3_TXD || UART3_TXD || F22 || O | ||

| + | |- | ||

| + | | 154 || UART4_CTS || UART4_CTS || L3 || O || rowspan=4|3.3V | ||

| + | |- | ||

| + | | 155 || UART4_RTS || UART4_RTS || L4 || I | ||

| + | |- | ||

| + | | 198 ||UART4_RXD|| '''KEY_ROW0''' || V6 || I | ||

| + | |- | ||

| + | | 199 ||UART4_TXD || '''KEY_COL0''' || W5 || O | ||

| + | |- | ||

| + | | 189 || UART5_CTS || '''KEY_ROW4''' || '''V5''' || O || rowspan=4|3.3V | ||

| + | |- | ||

| + | | 190 || UART5_RTS || '''KEY_COL4''' || '''T6''' || I | ||

| + | |- | ||

| + | | 196 || UART5_RXD|| '''KEY_ROW1''' || '''U6''' || I | ||

| + | |- | ||

| + | | 197 || UART5_TXD || '''KEY_COL1''' || '''U7'''|| O | ||

| + | |} | ||

| + | ===PWM功能=== | ||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | ! Pin Number !! Description !! CPU Pin Name !! CPU !! Direction !! 电压 | ||

| + | |- | ||

| + | |92 || PWM Function OUT 3 || PWM3_OUT || C20 || O || rowspan=2|3.3V | ||

| + | |- | ||

| + | | 89 || PWM Function OUT 4 || PWM4_OUT || B21 || O | ||

| + | |- | ||

| + | |} | ||

| + | <br/> | ||

2019年11月6日 (三) 11:25的最新版本

| Pin Number | CPU Pin Name | Description | Direction | 电压 |

|---|---|---|---|---|

| 2 | 5VIN | 核心板5V供电 | I | 5V |

| 4 | ||||

| 6 | ||||

| 8 | ||||

| 10 | ||||

| 12 | 3P3V | 评估板电源使能信号 | O | 3.3V |

| 14 | ||||

| 16 | ||||

| 28 | SW_IN | 开关机信号输入(MX6_ONOFF) | I | 3.3V |

| 休眠信号(GPIO_19) | I | |||

| 39 | PRO_B | 复位CPU | I | |

| 26 | VSNVS_3V0 | RTC电源 | I | 3V |

目录

电源

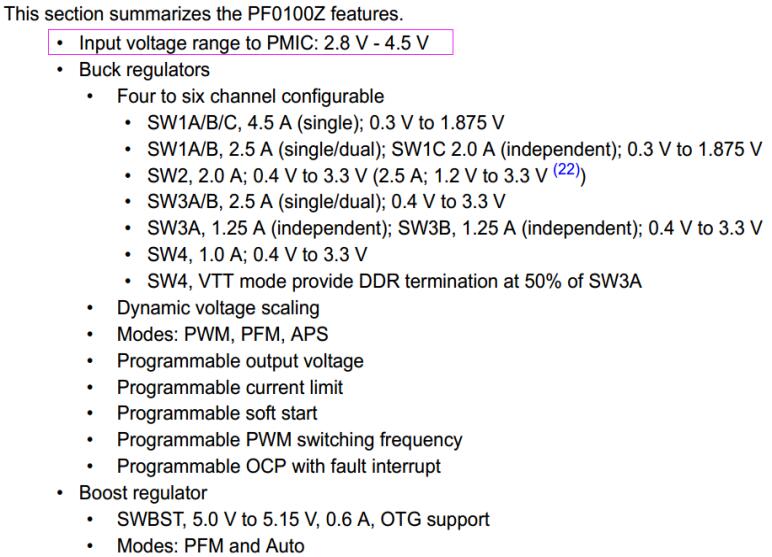

核心板使用PMIC(PF0100Z)来进行电源的管理,输入电压为:DC2.8V~4.5V,推荐使用4.2V。

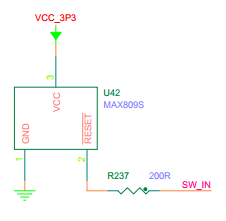

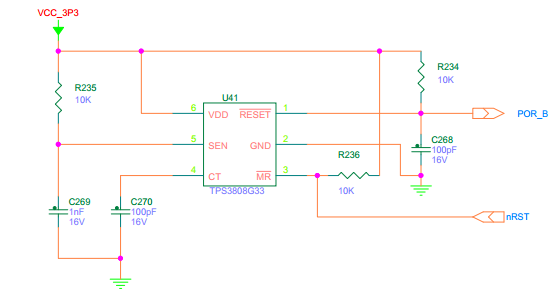

复位信号POR_B和开关机引脚SW_IN

复位信号POR_B在系统启动时必须拉高,如果需要手动复位,只需在推荐电路中的nRST引脚上使用一个连接到地的按键即。注意,复位信号是敏感信号,所以nRST引脚到按键的走线要尽量短,并且走线需作包地处理,避免干扰影像系统的稳定性。

开关机引脚SW_IN,可以对系统进行开关机操作和休眠唤醒操作, 系统休眠后,拉低此引脚,系统会进行唤醒操作; 长按此引脚,系统会关机,然后再长按此引脚,系统会开机。

以下为这两个引脚底板设计推荐电路图:

RTC电源

P3V3_LICELL此引脚为CPU内部RTC供电的引脚,可以使用外部电池供电(3V),也可以使用核心板上的PMIC来提供,使用这种方式的时候,需要设置PMIC来调整输出的电压。

USBOTG接口

核心板提供1路USB OTG和1路USB HOST信号,USB OTG用于固件的下载,USB HOST用于与外界的连接,诸如键盘、鼠标、U盘等。USB OTG必须引出,请使用者谨记。

USB OTG的供电(USB_OTG_VBUS)和USB HOST的供电(USB_H1_VBUS)需要外界来提供,电压为5V。

调试串口UART1

核心板使用UART1来作为调试串口,此接口作为打印调试信息的接口必须引出,请使用者谨记。

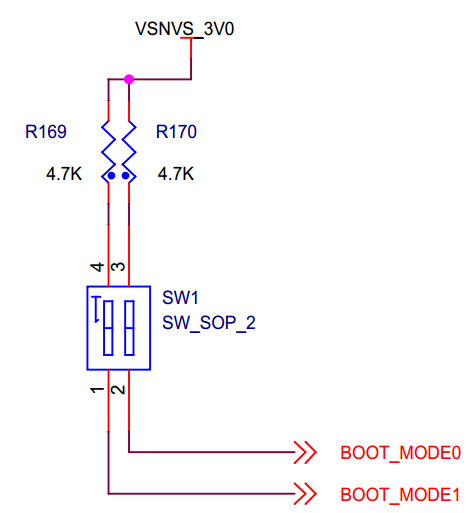

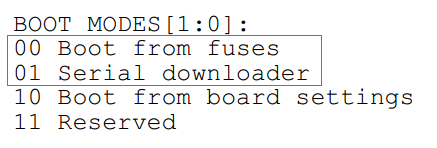

BOOT选择

核心板内部使用拨码开关的方式来进行BOOT的选择。 推荐将BOOT1拉低,然后使用拨码的方式来操作BOOT0,来选择是否进入烧录模式:

按下按键进入烧录模式;

松开按键系统通过设置好的熔丝方式启动。

目前核心板使用熔丝的方式来启动系统。

HDMI接口

| Pin Number | Description | CPU Pin Name | CPU | Direction | Voltage |

|---|---|---|---|---|---|

| 166 | Positive Data Signal 0 | HDMI_D0P | K6 | I/O | 2.5V |

| 165 | Negative Data Signal 0 | HDMI_D0M | K5 | I/O | |

| 168 | Positive Data Signal 1 | HDMI_D1P | J4 | I/O | |

| 167 | Negative Data Signal 1 | HDMI_D1M | J3 | I/O | |

| 170 | Positive Data Signal 02 | HDMI_D2P | K4 | I/O | |

| 169 | Negative Data Signal 2 | HDMI_D2M | K3 | I/O | |

| 164 | Positive Clock Signal | HDMI_CLKP | J6 | I | |

| 163 | Negative Clock Signal | HDMI_CLKM | J5 | I | |

| 171 | Hot Plug Detection Signal | HDMI_HPD | K1 | I/O | |

| 172 | CEC line between source and sink | HDMI_CEC_IN | W4 | I/O |

设计要求

HDMI的接口芯片要靠近HDMI接口,布局时要与接口在一条直线上,保证信号线短且直,为了避免信号不连续,走线拐角采用圆弧或者45度走线替代90度走线。尽量减少过孔数目,尽可能将过孔靠近HDMI连接器放置。几对差分信号要做等长,尽量做到1Mil的对内等长,组内严格等长。控制HDMI的差分信号对阻抗为100±15%ohm。

LVDS接口

| Pin Number | Description | CPU Pin Name | CPU | Direction | Voltage |

|---|---|---|---|---|---|

| 209 | LVDS0 Data Signals | LVDS0_TX0_P | U1 | I/O | 2.5V |

| 210 | LVDS0_TX0_N | U2 | I/O | ||

| 207 | LVDS0_TX1_P | U3 | I/O | ||

| 208 | LVDS0_TX1_N | U4 | I/O | ||

| 205 | LVDS0_TX2_P | V1 | I/O | ||

| 206 | LVDS0_TX2_N | V2 | I/O | ||

| 203 | LVDS0_TX3_P | W1 | I/O | ||

| 204 | LVDS0_TX3_N | W2 | I/O | ||

| 201 | LVDS0 Positive Clock Signal | LVDS0_CLK_P | V3 | I/O | |

| 202 | LVDS0 Negative Clock Signal | LVDS0_CLK_N | V4 | I/O | |

| 8 | LVDS1 Data Signals | LVDS1_TX0_P | Y2 | I/O | 2.5V |

| 7 | LVDS1_TX0_N | Y1 | I/O | ||

| 10 | LVDS1_TX1_P | AA1 | I/O | ||

| 9 | LVDS1_TX1_N | AA2 | I/O | ||

| 4 | LVDS1_TX2_P | AB2 | I/O | ||

| 3 | LVDS1_TX2_N | AB1 | I/O | ||

| 5 | LVDS1_TX3_P | AA4 | I/O | ||

| 6 | LVDS1_TX3_N | AA3 | I/O | ||

| 1 | LVDS1 Positive Clock Signal | LVDS1_CLK_P | Y4 | I/O | |

| 2 | LVDS1 Negative Clock Signal | LVDS1_CLK_N | Y3 | I/O |

设计要求

为了尽量减少偏差,LVDS差分对之间走线要求等长处理,组内尽量做到严格等长。尽量减少过孔及其它导致信号不连续的行为。任何寄生负载,如电容,必须等量存在于每对差分对中。为了避免信号不连续,走线拐角采用圆弧或者45度走线替代90度走线。控制LVDS的差分信号对阻抗为100±15%ohm。

RGB显示接口

LTT_MX6_SOM200系列核心板的RGB显示接口没有引出到邮票孔接口,而是引到板载的FPC连接器,以下为此连接器的序号定义:

| Pin Number | Description | CPU Pin Name | CPU | Direction | Voltage |

|---|---|---|---|---|---|

| 1 | 4.2V电源输入 | I | 4.2V | ||

| 2 | |||||

| 3 | IPU DISP Data Signal | DISP0_DAT0 | P24 | IO | 3.3V |

| 4 | DISP0_DAT1 | P22 | IO | ||

| 5 | DISP0_DAT2 | P23 | IO | ||

| 6 | DISP0_DAT3 | P21 | IO | ||

| 7 | DISP0_DAT4 | P20 | IO | ||

| 8 | DISP0_DAT5 | R25 | IO | ||

| 9 | DISP0_DAT6 | R23 | IO | ||

| 10 | DISP0_DAT7 | R24 | IO | ||

| 11 | DISP0_DAT8 | R22 | IO | ||

| 12 | DISP0_DAT9 | T25 | IO | ||

| 13 | DISP0_DAT10 | R21 | IO | ||

| 14 | DISP0_DAT11 | T23 | IO | ||

| 15 | DISP0_DAT12 | T24 | IO | ||

| 16 | DISP0_DAT13 | R20 | IO | ||

| 17 | DISP0_DAT14 | T2 | IO | ||

| 18 | DISP0_DAT15 | T22 | IO | ||

| 19 | DISP0_DAT16 | T21 | IO | ||

| 20 | DISP0_DAT17 | U24 | IO | ||

| 21 | DISP0_DAT18 | V25 | IO | ||

| 22 | DISP0_DAT19 | U23 | IO | ||

| 23 | DISP0_DAT20 | U22 | IO | ||

| 24 | DISP0_DAT21 | T20 | IO | ||

| 25 | DISP0_DAT22 | V24 | IO | ||

| 26 | DISP0_DAT23 | W24 | IO | ||

| 27 | IPU DISP Clk Signal | DISP0_CLK | N19 | O | |

| 28 | IPU DISP HSYNC Signal | DISP0_HSYNCH | N25 | O | |

| 29 | IPU DISP VSYNC Signal | DISP0_VSYNCH | N20 | O | |

| 30 | DISP0_CNTRST | DISP0_CNTRST | P38 | O | |

| 31 | IPU DISP Data Ready Signal | DISP0_DRDY | N21 | O | |

| 32 | DISP0_SYNC | DISP0_SYNC | E15 | O | |

| 33 | LVDS_PWM | LVDS_PWM | T2 | O | 3.3V |

| 34 | TOUCH_nINT | TOUCH_nINT | R6 | I | 3.3V |

| 35 | TOUCH_RST | TOUCH_RST | D16 | O | 3.3V |

| 36 | TOUCH_SCL | TOUCH_SCL | 连接至I2C3 | IO | 3.3V |

| 37 | TOUCH_SDA | TOUCH_SDA | IO | 3.3V | |

| 38 | 电源地 | I | 0V | ||

| 39 | |||||

| 40 | |||||

设计要求

组内信号线要求做等长处理。

SATA硬盘接口

| Pin Number | Description | CPU Pin Name | CPU | Direction | Voltage |

|---|---|---|---|---|---|

| 121 | Positive Receive Signal | SATA_RXP | B14 | I | 2.5V |

| 120 | Negative Receive Signal | SATA_RXN | A14 | I | |

| 122 | Positive Transmit Signal | SATA_TXP | A12 | O | |

| 123 | Negative Transmit Signal | SATA_TXN | B12 | O |

设计要求

SATA差分信号对之间走线要求做等长处理,采用尽可能小封装的耦合电容,电容的位置要尽量靠近连接器,差分信号的阻抗控制在100ohm。

USB接口

| Pin Number | Description | CPU Pin Name | CPU | Direction | Voltage |

|---|---|---|---|---|---|

| 131 | USB HOST | USB_H1_DN | F10 | IO | |

| 130 | USB_H1_DP | E10 | IO | ||

| 135 | USB OTG | USB_OTG_DN | B6 | IO | |

| 134 | USB_OTG_DP | A6 | IO | ||

| 132 | USB_OTG_ID | GPIO01 | T4 | I | 3.3V |

| 14 | ENET_RX_ER | W23 | |||

| 49 | USB_OTG_OC | EIM_DATA21 | H20 | I | |

| 190 | KEY_COL4 | T6 | |||

| 61 | USB_OTG_PWR | EIM_DATA22 | E23 | O | |

| 189 | KEY_ROW4 | V5 |

设计要求

尽可能缩短走线长度,尽可能的减少在USB高速信号线上的过孔数和拐角,从而可以更好的做到阻抗的控制,避免信号的反射。在布线时,要做到差分信号走线的长度匹配。控制USB差分信号对之间的布线间距,要确保90 ohm的差分阻抗。

SD接口

| Pin Number | Description | CPU Pin Name | CPU | Direction | Voltage |

|---|---|---|---|---|---|

| 89 | SD1 Signal | SD1_CMD | B21 | I | 3.3V |

| 90 | SD1_CLK | D20 | O | ||

| 91 | SD1_DATA0 | A21 | IO | ||

| 92 | SD1_DATA1 | C20 | IO | ||

| 93 | SD1_DATA2 | E19 | IO | ||

| 94 | SD1_DATA3 | F18 | IO | ||

| 83 | SD2 Signal | SD2_CMD | F19 | IO | 3.3V |

| 84 | SD2_CLK | SD2_CLK | O | ||

| 85 | SD2_DATA0 | A22 | IO | ||

| 86 | SD2_DATA1 | E20 | IO | ||

| 87 | SD2_DATA2 | A23 | IO | ||

| 88 | SD2_DATA3 | B22 | IO | ||

| 110 | SD3 Signal | SD3_CMD | B13 | IO | 3.3V |

| 109 | SD3_CLK | D14 | O | ||

| 111 | SD3_DATA0 | E14 | IO | ||

| 112 | SD3_DATA1 | F14 | IO | ||

| 113 | SD3_DATA2 | A15 | IO | ||

| 114 | SD3_DATA3 | B15 | IO | ||

| 115 | SD3_DATA4 | D13 | IO | ||

| 116 | SD3_DATA5 | C13 | IO | ||

| 117 | SD3_DATA6 | E13 | IO | ||

| 118 | SD3_DATA7 | F13 | IO |

PCIE接口

| Pin Number | Description | CPU Pin Name | CPU | Direction | Voltage |

|---|---|---|---|---|---|

| 141 | Positive Receive Signal | PCIE_RXP | B2 | I | 2.5V |

| 140 | Negative Receive Signal | PCIE_RXM | B1 | I | |

| 139 | Positive Transmit Signal | PCIE_TXP | B3 | O | |

| 138 | Negative Transmit Signal | PCIE_TXM | A3 | O |

设计要求

PCIE信号为差分信号,布线时要注意减少有害串扰的影响和电磁干扰(EMI)的影响。

AUD音频接口

核心板提供音频信号,可以使用WM8962芯片进行音频编解码,这是一款低功耗、高性能的立体音频编解码器。它支持单端输入,录音通道支持自动增量控制(AGC),且内置滤波电路。同时支持两路单端输出和两路差分高功率输出。I2C信号用于配置芯片寄存器,I2S用于音频数据传输,系统默认使用I2C1和I2S3来连接WM8962,如需使用请参照我司的参考设计,请使用者谨记。

| Pin Number | Description | CPU Pin Name | CPU | Direction | Voltage |

|---|---|---|---|---|---|

| 179 | AUD3 Signal | AUD3_TXC | N1 | IO | 1.8V |

| 178 | AUD3_TXFS | N4 | IO | ||

| 180 | AUD3_TXD | P2 | IO | ||

| 177 | AUD3_RXD | N3 | IO | ||

| 83 | AUD4_RXC | SD2_CMD | F19 | IO | 3.3V |

| 85 | AUD4_RXC | SD2_DATA0 | A22 | IO | |

| 84 | AUD4_RXC | SD2_CLK | C21 | IO | |

| 88 | AUD4_TXC | SD2_DATA3 | B22 | IO | |

| 87 | AUD4_TXD | SD2_DATA2 | A23 | IO | |

| 86 | AUD4_TXFS | SD2_DATA1 | E20 | IO | |

| 58 | AUD5_RXC | EIM_DATA25 | G22 | IO | |

| 196 | AUD5_RXD | KEY_ROW1 | U6 | IO | |

| 60 | AUD5_RXFS | EIM_DATA24 | F22 | IO | |

| 199 | AUD5_TXC | KEY_COL0 | W5 | IO | |

| 198 | AUD5_TXD | KEY_ROW0KEY_COL1 | V6 | IO | |

| 197 | AUD5_TXFS | KEY_COL1 | U7 | IO |

设计要求

保持音频信号线尽可能短,并尽量远离干扰源,信号线做到组内等长。

百兆以太网接口

LTT_MX6_SOM200核心板引出两组以太网的接口,分别为百兆以太网和千兆以太网接口,由于IMX6系列的芯片不支持百兆以太网和千兆以太网同时使用,所以目前两种接口同时只能使用一种,请使用者多加注意。

| Pin Number | Description | CPU Pin Name | CPU | Direction | Voltage |

|---|---|---|---|---|---|

| 19 | ENET_MDC | ENET_MDC | V20 | O | 3.3V |

| 16 | ENET_MDIO | ENET_MDIO | V23 | IO | |

| 18 | Enet Signal | ENET_RXD0 | W21 | I | |

| 13 | ENET_RXD1 | W22 | I | ||

| 21 | ENET_CRS_DV | U21 | I | ||

| 22 | ENET_TXD0 | U20 | O | ||

| 17 | ENET_TXD1 | W20 | O | ||

| 20 | ENET_TX_EN | V21 | O | ||

| 182 | ENET_nRST | R1 | O | ||

| 15 | ENET_REF_CLK | V22 | O | ||

| 107 | ENET_nINT | A16 | I |

千兆以太网接口

LTT_MX6_SOM200核心板引出两组以太网的接口,分别为百兆以太网和千兆以太网接口,由于IMX6系列的芯片不支持百兆以太网和千兆以太网同时使用,所以目前两种接口同时只能使用一种,请使用者多加注意。

| Pin Number | Description | CPU Pin Name | CPU | Direction | Voltage |

|---|---|---|---|---|---|

| 71 | RGMII Signal | RGMII_RXD3 | D23 | I | 1.5V |

| 72 | RGMII_RXDV | D22 | I | ||

| 73 | RGMII_TXEN | C23 | O | ||

| 74 | RGMII_TXD0 | C22 | O | ||

| 75 | RGMII_TXD1 | F20 | O | ||

| 76 | RGMII_TXD2 | E21 | O | ||

| 77 | RGMII_TXCLK | D21 | O | ||

| 78 | RGMII_RXD0 | C24 | I | ||

| 79 | RGMII_RXCLK | B25 | O | ||

| 80 | RGMII_RXD2 | B24 | I | ||

| 81 | RGMII_TXD3 | D23 | O | ||

| 82 | RGMII_RXD1 | B23 | O |

设计要求:

保持RGMII信号线尽可能短,并尽量远离干扰源,信号线做到组内等长。

CAN总线接口

| Pin Number | Description | CPU Pin Name | CPU | Direction | Voltage |

|---|---|---|---|---|---|

| 191 | CAN1_RX | GPIO08 | R5 | I | 3.3V |

| 192 | CAN1_TX | GPIO07 | R3 | O | |

| 189 | CAN2_RX | KEY_ROW4 | V5 | I | |

| 190 | CAN2_TX | KEY_COL4 | T6 | O |

设计要求:

布线时要注意控制收发器转换后差分对信号等长。注意给CAN总线匹配终端电阻。

SPI接口

| Pin Number | Description | CPU Pin Name | CPU | Direction | Voltage |

|---|---|---|---|---|---|

| 63 | CSPI2_MISO | EIM_OE | J24 | IO | 3.3V |

| 53 | CSPI2_MOSI | EIM_CS1 | J23 | IO | |

| 50 | CSPI2_RDY | EIM_A25 | H19 | I | |

| 62 | CSPI2_CLK | EIM_CS0 | H24 | IO | |

| 46 | CSPI2_CS0 | EIM_RW | K20 | IO | |

| 52 | CSPI2_CS1 | EIM_LBA | K22 | IO | |

| 61 | CSPI4_MISO | EIM_D22 | E23 | IO | 3.3V |

| 57 | CSPI4_MOSI | EIM_D28 | G23 | IO | |

| 59 | CSPI4_RDY | EIM_EB3 | F23 | I | |

| 49 | CSPI4_CLK | EIM_D21 | H20 | IO | |

| 48 | CSPI4_CS0 | EIM_DATA29 | J19 | IO | |

| 60 | CSPI4_CS2 | EIM_DATA24 | F22 | IO | |

| 58 | CSPI4_CS3 | EIM_DATA25 | G22 | IO |

12C接口

| Pin Number | Description | CPU Pin Name | CPU | Direction | Voltage |

|---|---|---|---|---|---|

| 175 | I2C1 Serial Data | I2C1_SDA | N6 | IO | 1.8V |

| 176 | I2C1 Serial Clock | I2C1_SCL | N5 | IO | |

| 187 | I2C2 Serial Data | I2C2_SDA | T7 | IO | 3.3V |

| 188 | I2C2 Serial Clock | I2C2_SCL | U5 | IO | |

| 194 | I2C3 Serial Data | I2C3_SDA | T3 | IO | 3.3V |

| 195 | I2C3 Serial Clock | I2C3_SCLL | R7 | IO |

CSI摄像头接口

| Pin Number | Description | CPU Pin Name | CPU | Direction | 电压 |

|---|---|---|---|---|---|

| 107 | IPU CSI Data Signal | CSIO_DAT12 | M2 | I | 2.5V |

| 105 | CSIO_DAT13 | L1 | I | ||

| 99 | CSIO_DAT14 | M4 | I | ||

| 115 | CSIO_DAT15 | M5 | I | ||

| 97 | CSIO_DAT16 | L4 | I | ||

| 95 | CSIO_DAT17 | L3 | I | ||

| 103 | CSIO_DAT18 | M6 | I | ||

| 101 | CSIO_DAT19 | L6 | I | ||

| 113 | IPU CSI Hsync Signal | CSI0_HSYNCH | P4 | I | |

| 109 | IPU CSI Vsync Signal | CSI0_VSYNCH | N2 | I | |

| 111 | IPU CSI Pixclk Signal | CSI0_PIXCLK | P1 | I |

设计要求

CSI-MCLK和CSI-PCLK需要各自包地,并保证较少的换层连接到摄像头连接器,保证连接器周围信号地的完整性

MIPI摄像头接口

| Pin Number | Description | CPU Pin Name | CPU | Direction | 电压 |

|---|---|---|---|---|---|

| 141 | D-Phy Differential Data | CSI_D3M | F2 | IO | 2.5V |

| 142 | CSI_D3P | F1 | IO | ||

| 143 | CSI_D2M | E1 | IO | ||

| 144 | CSI_D2P | E2 | IO | ||

| 145 | CSI_D1M | D1 | IO | ||

| 146 | CSI_D1P | D2 | IO | ||

| 147 | CSI_D0M | E4 | IO | ||

| 148 | CSI_D0P | E3 | IO | ||

| 149 | D-Phy Differential Clock | CSI_CLKM | F4 | IO | |

| 150 | CSI_CLKP | F3 | IO |

设计要求

MIPI信号线下方一定要有参考层(推荐用地层),且一定要保证参考层的连续性。MIPI线对之间以及线对与线对之间的长度误差注意控制,MIPI信号线尽量不要打过孔。

UART接口

| Pin Number | Description | CPU Pin Name | CPU | Direction | 电压 |

|---|---|---|---|---|---|

| 173 | UART1_RX | UART1_RX | M3 | I | 1.8V |

| 174 | UART1_TX | UART1_TX | M1 | O | |

| 57 | UART2_CTS | EIM_D28 | G23 | O | 3.3V |

| 48 | UART2_RTS | EIM_D29 | J19 | I | |

| 68 | UART2_RXD | EIM_D27 | E25 | I | |

| 69 | UART2_TXD | EIM_D26 | E24 | O | |

| 70 | UART3_CTS | EIM_D23 | D25 | O | 3.3V |

| 44 | UART3_RTS | EIM_D31 | H21 | I | |

| 58 | UART3_RXD | UART3_RXD | G22 | I | |

| 60 | UART3_TXD | UART3_TXD | F22 | O | |

| 154 | UART4_CTS | UART4_CTS | L3 | O | 3.3V |

| 155 | UART4_RTS | UART4_RTS | L4 | I | |

| 198 | UART4_RXD | KEY_ROW0 | V6 | I | |

| 199 | UART4_TXD | KEY_COL0 | W5 | O | |

| 189 | UART5_CTS | KEY_ROW4 | V5 | O | 3.3V |

| 190 | UART5_RTS | KEY_COL4 | T6 | I | |

| 196 | UART5_RXD | KEY_ROW1 | U6 | I | |

| 197 | UART5_TXD | KEY_COL1 | U7 | O |

PWM功能

| Pin Number | Description | CPU Pin Name | CPU | Direction | 电压 |

|---|---|---|---|---|---|

| 92 | PWM Function OUT 3 | PWM3_OUT | C20 | O | 3.3V |

| 89 | PWM Function OUT 4 | PWM4_OUT | B21 | O |