LTT-MX6-SOM100

产品介绍

i.mx6核心板是一款基于NXP ARM Cortex -A9架构处理器研发设计的核心板,是一个可运行Android、Liux系统的最小硬件平台。运行频率达1.0GHZ、带有512KB L2缓存和64位DDR3或2通道、32位LPDDR2支持。该器件集成了FlexCAN和MLB总线、PCL Express、LVDS、还支持MIPI摄像头和显示器以及HDMI V1.4,拥有商业级、加强商业级,工业级以及车规级多种环境温度可选;核心板采用金手指方式,更小的尺寸方便用户开发与更换;拥有20多种接口协议,非常适合消费电子、汽车和工业控制以多媒体为中心的应用。提供全面的技术支持和长期的售后服务,全力协助客户产品开发,无后顾之忧。

- CPU:i.mx6系列

- DDR:DDR3 1GB(可扩展2GB)

- Flash: 8GB EMMC(可扩展64GB)、NorFLASH

- Temperature:工业级 -40 ~ 105℃

- 存储: SD/MMC CARD,4Bit ; SATA II,3.0Gbps

- USB: USB OTG;USB HOST

- 显示: HDMI;LVDS x 2路/8bit;RGB,24Bit

- 摄像头: CSI 8Bit;MIPI 2 Lanes;PCL Express

- 以太网: 10/100M

- PCL Express: Gen2.0

- UART: 5路TTL

- CSPI: 2路

- CAN: 2路

- 12C: 3路

- 音频: AUD,2路

- PWM:3 路

- IO: 多路复用可配置

- WTD: 1路

- SDIO: 2路

- 启动开关: 1路

最小系统设计要求

| Pin Number | CPU Pin Name | Description | Direction | 电压 |

|---|---|---|---|---|

| 2 | 5VIN | 核心板5V供电 | I | 5V |

| 4 | ||||

| 6 | ||||

| 8 | ||||

| 10 | ||||

| 12 | 3P3V | 评估板电源使能信号 | O | 3.3V| |

| 14 | ||||

| 16 | ||||

| 28 | SW_IN | 开关机信号输入(MX6_ONOFF) | I | 3.3V |

| 休眠信号(GPIO_19) | I | |||

| 39 | PRO_B | 复位CPU | I | |

| 26 | VSNVS_3V0 | RTC电源 | I | 3V |

- 电源

核心板使用DC降压芯片(RT8070)来进行电源的管理,输入电压为:DC4.1V~5.5V,推荐使用5V。

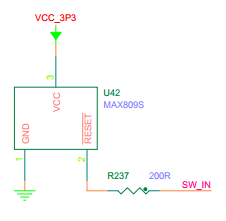

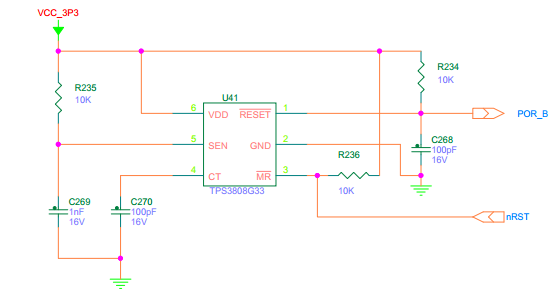

- 复位信号POR_B和开关机引脚SW_IN

复位信号POR_B在系统启动时必须拉高,如果需要手动复位,只需在推荐电路中的nRST引脚上使用一个连接到地的按键即。注意,复位信号是敏感信号,所以nRST引脚到按键的走线要尽量短,并且走线需作包地处理,避免干扰影像系统的稳定性。

开关机引脚SW_IN,可以对系统进行开关机操作和休眠唤醒操作, 系统休眠后,拉低此引脚,系统会进行唤醒操作; 长按此引脚,系统会关机,然后再长按此引脚,系统会开机。

以下为这两个引脚底板设计推荐电路图:

- RTC电源

VSNVS_3V0此引脚为CPU内部RTC供电的引脚,可以使用外部电池供电(3V),此处的电源还用于核心板内部BOOT上拉,如不使用外部的电池,需外部供电,电平3V或者3.3V也可。

- USBOTG接口

核心板提供1路USB OTG和1路USB HOST信号,USB OTG用于固件的下载,USB HOST用于与外界的连接,诸如键盘、鼠标、U盘等。USB OTG必须引出,请使用者谨记。

USB OTG的供电(USB_OTG_VBUS)和USB HOST的供电(USB_H1_VBUS)需要外界来提供,电压为5V。

- 调试串口UART1

核心板使用UART1来作为调试串口,此接口作为打印调试信息的接口必须引出,请使用者谨记。

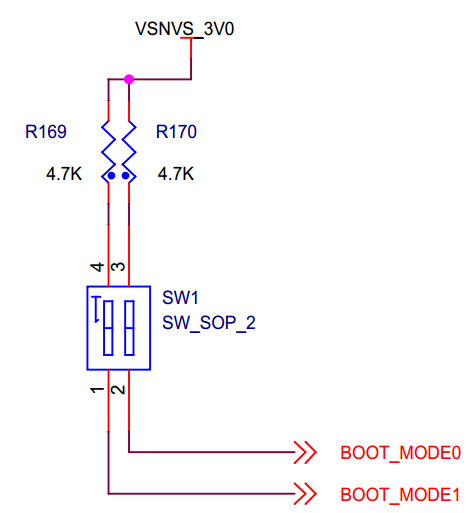

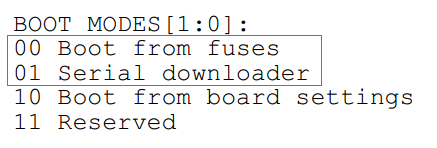

- BOOT选择

核心板内部使用拨码开关的方式来进行BOOT的选择。 推荐将BOOT1拉低,然后使用拨码的方式来操作BOOT0,来选择是否进入烧录模式:

按下按键进入烧录模式;

松开按键系统通过设置好的熔丝方式启动。

目前核心板使用熔丝的方式来启动系统。

- 功能模块接口

LTT_MX6_SOM100系列核心板采用了灵活的开关机方式,并且针对低功耗的要求添加了对评估板电源的控制信号,用户可以根据需要自行设计。(注意:默认使用的管脚以灰色填充。)

- 电源接口

| Pin Number | CPU Pin Name | Description | Direction | 电压 |

|---|---|---|---|---|

| 2 | 5V_IN | 核心板5V供电 | I | 5V |

| 4 | ||||

| 6 | ||||

| 8 | ||||

| 10 | ||||

| 12 | PWR_EN | 评估板电源使能信号 | O | 3.3V |

| 14 | ||||

| 20 |

- HDMI接口

| Pin Number | Description | CPU Pin Name | CPU | Direction | Voltage |

|---|---|---|---|---|---|

| 102 | Positive Data Signal 0 | HDMI_D0P | K6 | I/O | 2.5 |

| 104 | Negative Data Signal 0 | HDMI_D0M | K5 | I/O | |

| 94 | Positive Data Signal 1 | HDMI_D1P | J4 | I/O | |

| 96 | Negative Data Signal 1 | HDMI_D1M | J3 | I/O | |

| 86 | Positive Data Signal 02 | HDMI_D2P | K4 | I/O | |

| 88 | Negative Data Signal 2 | HDMI_D2M | K3 | I/O | |

| 98 | Positive Clock Signal | HDMI_CLKP | J6 | I | |

| 100 | Negative Clock Signal | HDMI_CLKM | J5 | I | |

| 92 | Hot Plug Detection Signal | HDMI_HPD | K1 | I/O | |

| 90 | CEC line between source and sink | HDMI_CEC_IN | W4 | I/O |

- 设计要求

HDMI的接口芯片要靠近HDMI接口,布局时要与接口在一条直线上,保证信号线短且直,为了避免信号不连续,走线拐角采用圆弧或者45度走线替代90度走线。尽量减少过孔数目,尽可能将过孔靠近HDMI连接器放置。几对差分信号要做等长,尽量做到1Mil的对内等长,组内严格等长。控制HDMI的差分信号对阻抗为100±15%ohm。

- LVDS接口

| Pin Number | Description | CPU Pin Name | CPU | Direction | Voltage |

|---|---|---|---|---|---|

| 135 | LVDS0 Data Signals | LVDS0_TX0_P | U1 | I/O | 2.5 |

| 133 | LVDS0_TX0_N | U2 | I/O | ||

| 147 | LVDS0_TX1_P | U3 | I/O | ||

| 145 | LVDS0_TX1_N | U4 | I/O | ||

| 129 | LVDS0_TX2_P | V1 | I/O | ||

| 131 | LVDS0_TX2_N | V2 | I/O | ||

| 139 | LVDS0_TX3_P | W1 | I/O | ||

| 137 | LVDS0_TX3_N | W2 | I/O | ||

| 143 | LVDS0 Positive Clock Signal | LVDS0_CLK_P | V3 | I/O | |

| 141 | LVDS0 Negative Clock Signal | LVDS0_CLK_N | V4 | I/O | |

| 134 | LVDS1 Data Signals | LVDS1_TX0_P | Y2 | I/O | 2.5 |

| 136 | LVDS1_TX0_N | Y1 | I/O | ||

| 132 | LVDS1_TX1_P | AA1 | I/O | ||

| 130 | LVDS1_TX1_N | AA2 | I/O | ||

| 142 | LVDS1_TX2_P | AB2 | I/O | ||

| 144 | LVDS1_TX2_N | AB1 | I/O | ||

| 140 | LVDS1_TX3_P | AA4 | I/O | ||

| 138 | LVDS1_TX3_N | AA3 | I/O | ||

| 148 | LVDS1 Positive Clock Signal | LVDS1_CLK_P | Y4 | I/O | |

| 146 | LVDS1 Negative Clock Signal | LVDS1_CLK_N | Y3 | I/O |

- 设计要求

为了尽量减少偏差,LVDS差分对之间走线要求等长处理,组内尽量做到严格等长。尽量减少过孔及其它导致信号不连续的行为。任何寄生负载,如电容,必须等量存在于每对差分对中。为了避免信号不连续,走线拐角采用圆弧或者45度走线替代90度走线。控制LVDS的差分信号对阻抗为100±15%ohm。

- RGB显示接口

| Pin Number | Description | CPU Pin Name | CPU | Direction | Voltage |

|---|---|---|---|---|---|

| 197 | IPU DISP Data Signal | DISP0_DAT0 | P24 | IO | 3.3V |

| 171 | DISP0_DAT1 | P22 | IO | ||

| 170 | DISP0_DAT2 | P23 | IO | ||

| 169 | DISP0_DAT3 | P21 | IO | ||

| 174 | DISP0_DAT4 | P20 | IO | ||

| 193 | DISP0_DAT5 | R25 | IO | ||

| 166 | DISP0_DAT6 | R23 | IO | ||

| 195 | DISP0_DAT7 | R24 | IO | ||

| 167 | DISP0_DAT8 | R22 | IO | ||

| 189 | DISP0_DAT9 | T25 | IO | ||

| 172 | DISP0_DAT10 | R21 | IO | ||

| 161 | DISP0_DAT11 | T23 | IO | ||

| 191 | DISP0_DAT12 | T24 | IO | ||

| 165 | DISP0_DAT13 | R20 | IO | ||

| 185 | DISP0_DAT14 | T2 | IO | ||

| 163 | DISP0_DAT15 | T22 | IO | ||

| 157 | DISP0_DAT16 | T21 | IO | ||

| 187 | DISP0_DAT17 | U24 | IO | ||

| 181 | DISP0_DAT18 | V25 | IO | ||

| 162 | DISP0_DAT19 | U23 | IO | ||

| 164 | DISP0_DAT20 | U22 | IO | ||

| 168 | DISP0_DAT21 | T20 | IO | ||

| 183 | DISP0_DAT22 | V24 | IO | ||

| 159 | DISP0_DAT23 | W24 | IO | ||

| 179 | IPU DISP Clk Signal | DISP0_CLK | N19 | O | |

| 199 | IPU DISP HSYNC Signal | DISP0_HSYNCH | N25 | O | |

| 175 | IPU DISP VSYNC Signal | DISP0_VSYNCH | N20 | O | |

| 173 | IPU DISP Data Ready Signal | DISP0_DRDY | N21 | O |

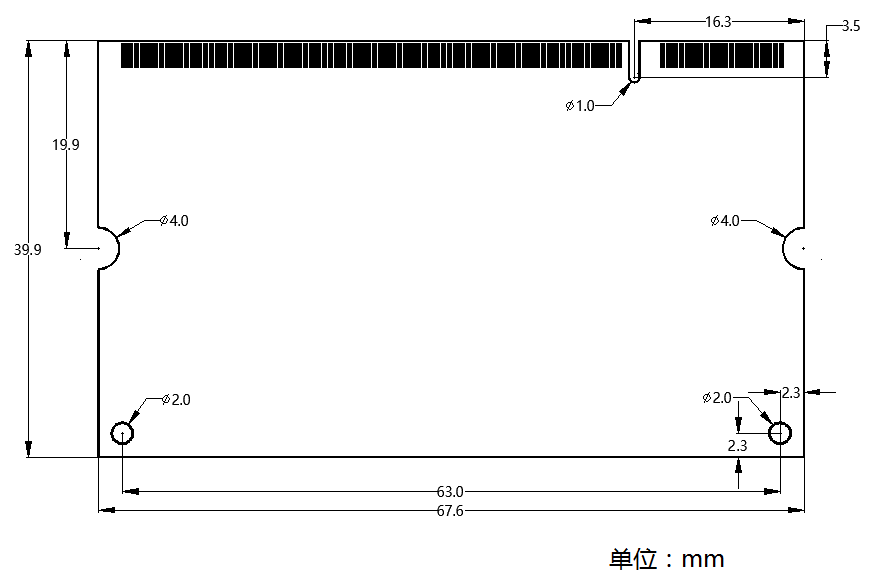

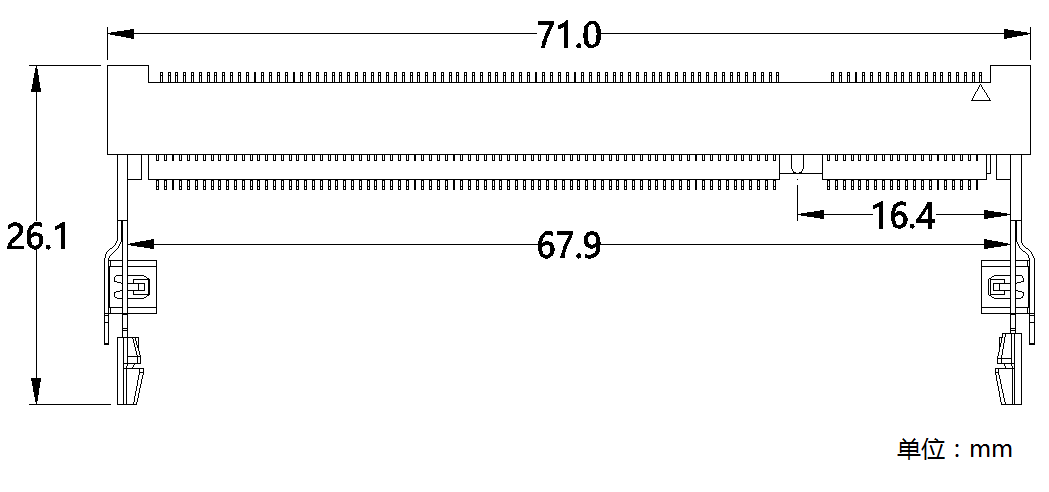

核心板机械尺寸图