“LTT-MX6-SOM100”的版本间的差异

跳到导航

跳到搜索

(→产品介绍) |

|||

| (未显示3个用户的16个中间版本) | |||

| 第1行: | 第1行: | ||

=== 产品介绍 === | === 产品介绍 === | ||

| − | + | LTT-MX6-SOM100核心板是一款基于NXP ARM®Cortex® -A9架构处理器研发设计的核心板,是一个可运行Android、Liux系统的最小硬件平台。运行频率达1.0GHZ、带有512KB L2缓存和64位DDR3或2通道、32位LPDDR2支持。 | |

| + | <br/> | ||

| + | 该核心板集成了FlexCAN和MLB总线、PCL Express、LVDS、还支持MIPI摄像头和显示器以及HDMI V1.4,拥有商业级、加强商业级,工业级以及车规级多种环境温度可选;核心板采用金手指方式,更小的尺寸方便用户开发与更换;拥有20多种接口协议,非常适合消费电子、汽车和工业控制以多媒体为中心的应用。提供全面的技术支持和长期的售后服务,全力协助客户产品开发,无后顾之忧。 | ||

[[文件:MX6-SOM100.png|300px]] | [[文件:MX6-SOM100.png|300px]] | ||

| 第6行: | 第8行: | ||

<br/> | <br/> | ||

---- | ---- | ||

| − | * | + | |

| − | * | + | ===资源介绍=== |

| − | * | + | *CPU:NXP Cortex™-A9 i.MX6(单、双、四核可选) |

| − | * | + | *GPU:Vivante GC2000 / NEON SIMD |

| − | + | *DDR:2GB(可选) | |

| − | * | + | *Flash:eMMC 8G (可选,最大128G) |

| − | * | + | *PWM Out:2 |

| − | * | + | *I2C:I2C x 3 |

| − | * | + | *SPI:SPI x 2 |

| − | * | + | *GPIO:10 |

| − | * | + | *PCM:PCM x 3 |

| − | * | + | *CSI:CSI x 1 |

| − | * | + | *SDIO:SDIO x 3 |

| − | * | + | *UART:TTL x 5 |

| − | * | + | *CAN BUS:CAN x 2 |

| − | * | + | *SATA:SATA-II x 1 |

| − | * | + | *PCI-e:PCI-e2.0 x 1 |

| − | * | + | *USB:HOST x 4、OTG x 1 |

| − | * | + | *ETHERNET:MII |

| − | * | + | *Display:LVDS0 x 1、LVDS1 x 1、RGB x 1、HDMI x 1 |

| − | * | + | *MIPI-CSI:MIPI-CSI2(4 lanes),可匹配AHD6324、MAX9286、ADV7180、ISL79985等芯片 |

| − | + | *Power:DC5V | |

| + | *Temperature:Work -20 ~ 75,Storage -40 ~ 85;可选工业级、车轨级 | ||

| + | *os:Android 4.4.2、Linux3.0.35、Linux3.14.52 | ||

---- | ---- | ||

| − | === | + | === 硬件设计要求 === |

| + | 底板设计要求请参考:[[LTT-MX6-SOM100硬件设计指导]] | ||

| + | <br> | ||

| + | 管脚说明请参考:[[LTT-MX6-SOM100管脚说明]] | ||

| − | |||

| − | + | ---- | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | === 核心板机械尺寸图 === | |

| − | + | [[文件:JXCCT.png|400px]] | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | [[文件: | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | [[文件:JXKCT.png|400px]] | |

| − | [[文件: | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | [[ | + | ===技术支持声明=== |

| + | 用户使用前请查阅[[技术支持声明|《技术支持声明》]] | ||

2020年1月2日 (四) 10:05的最新版本

产品介绍

LTT-MX6-SOM100核心板是一款基于NXP ARM®Cortex® -A9架构处理器研发设计的核心板,是一个可运行Android、Liux系统的最小硬件平台。运行频率达1.0GHZ、带有512KB L2缓存和64位DDR3或2通道、32位LPDDR2支持。

该核心板集成了FlexCAN和MLB总线、PCL Express、LVDS、还支持MIPI摄像头和显示器以及HDMI V1.4,拥有商业级、加强商业级,工业级以及车规级多种环境温度可选;核心板采用金手指方式,更小的尺寸方便用户开发与更换;拥有20多种接口协议,非常适合消费电子、汽车和工业控制以多媒体为中心的应用。提供全面的技术支持和长期的售后服务,全力协助客户产品开发,无后顾之忧。

资源介绍

- CPU:NXP Cortex™-A9 i.MX6(单、双、四核可选)

- GPU:Vivante GC2000 / NEON SIMD

- DDR:2GB(可选)

- Flash:eMMC 8G (可选,最大128G)

- PWM Out:2

- I2C:I2C x 3

- SPI:SPI x 2

- GPIO:10

- PCM:PCM x 3

- CSI:CSI x 1

- SDIO:SDIO x 3

- UART:TTL x 5

- CAN BUS:CAN x 2

- SATA:SATA-II x 1

- PCI-e:PCI-e2.0 x 1

- USB:HOST x 4、OTG x 1

- ETHERNET:MII

- Display:LVDS0 x 1、LVDS1 x 1、RGB x 1、HDMI x 1

- MIPI-CSI:MIPI-CSI2(4 lanes),可匹配AHD6324、MAX9286、ADV7180、ISL79985等芯片

- Power:DC5V

- Temperature:Work -20 ~ 75,Storage -40 ~ 85;可选工业级、车轨级

- os:Android 4.4.2、Linux3.0.35、Linux3.14.52

硬件设计要求

底板设计要求请参考:LTT-MX6-SOM100硬件设计指导

管脚说明请参考:LTT-MX6-SOM100管脚说明

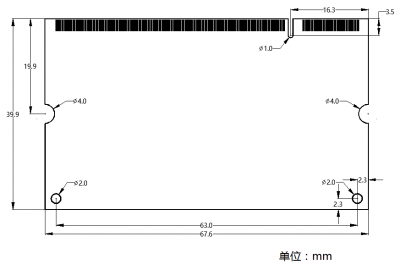

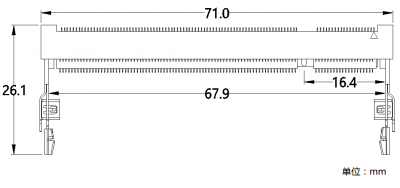

核心板机械尺寸图

技术支持声明

用户使用前请查阅《技术支持声明》